# French Contribution To The Construction Of SKA-MID

Stéphane Gauffre

SKA-France Day 2022

November 10<sup>th</sup>, 2022

- □ Receiver overview

- □ First Design

- □ New Design

- Development plan

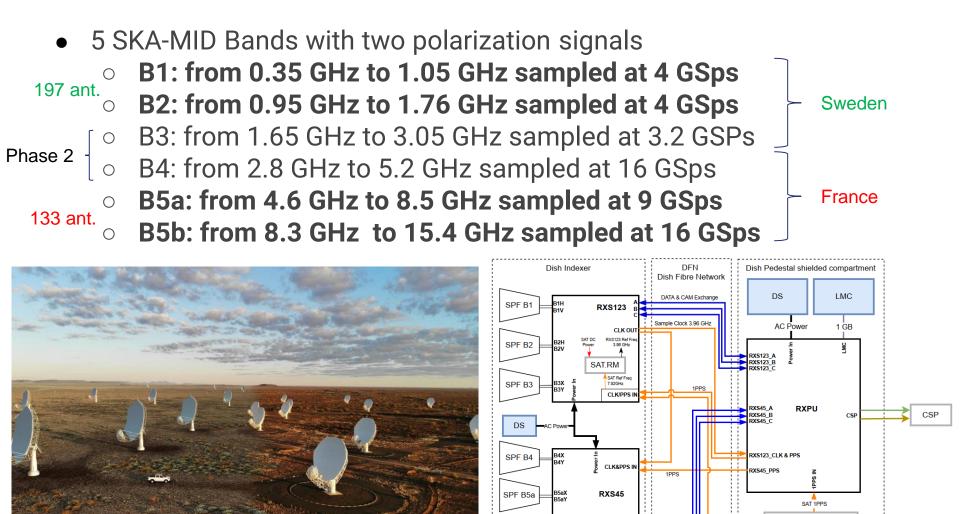

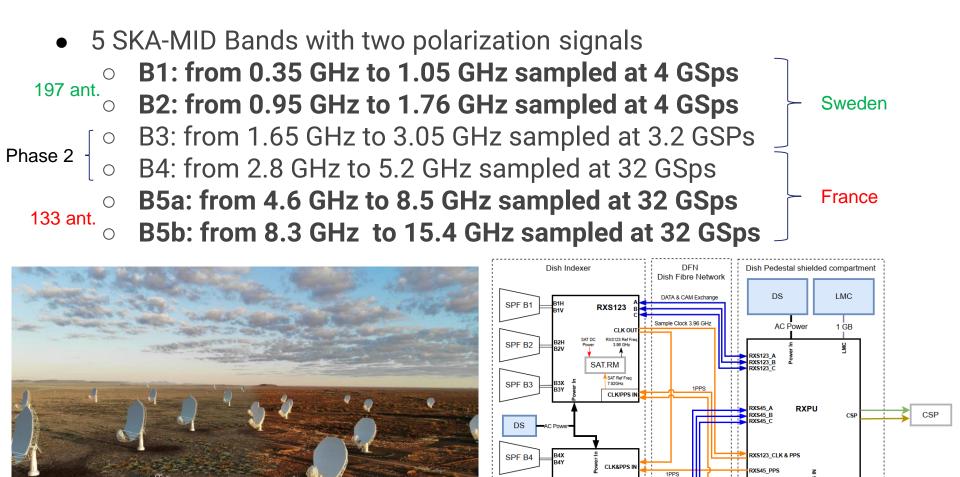

# **Receiver overview**

SPF B5b

SAT

SAT Ref Fred 7 92 GH

### **Receiver overview**

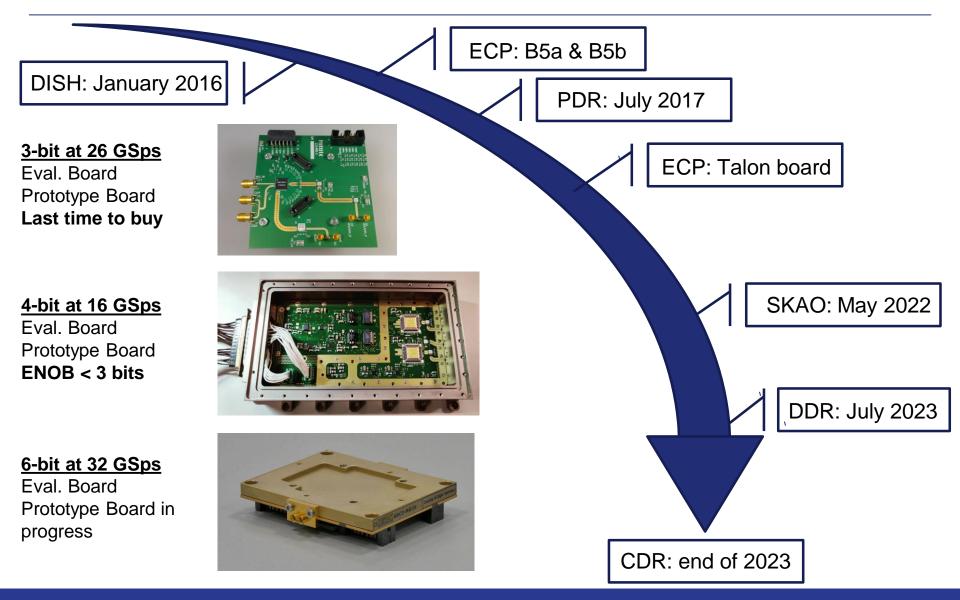

# **Development Phase**

# **First Design**

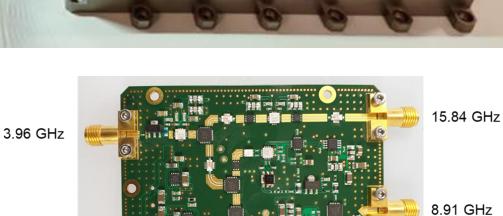

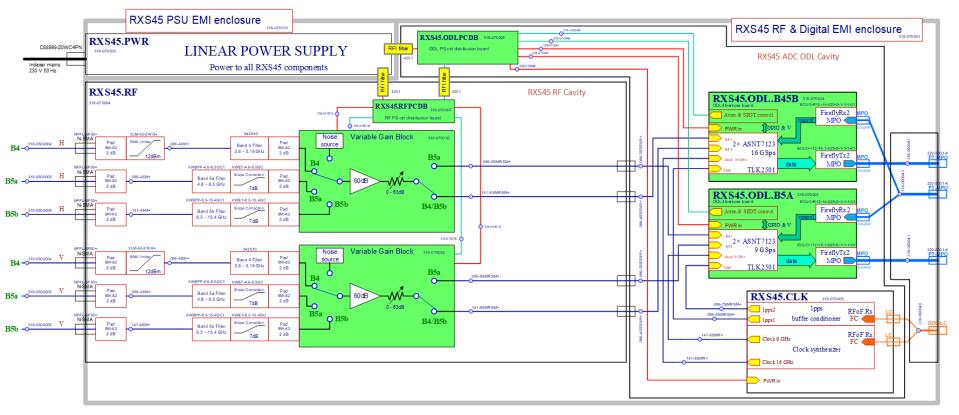

- Based on 4-bit ADC at 16 GSps

- Two ADC boards (B5a at 9 GSps and B5b at 16 GSps)

- Two RF boards with two outputs (one per band)

- > Two sampling clocks (9 GHz and 16 GHz)

Stéphane Gauffre

#### SKA-France Day 2022

#### November 10<sup>th</sup>, 2022 7

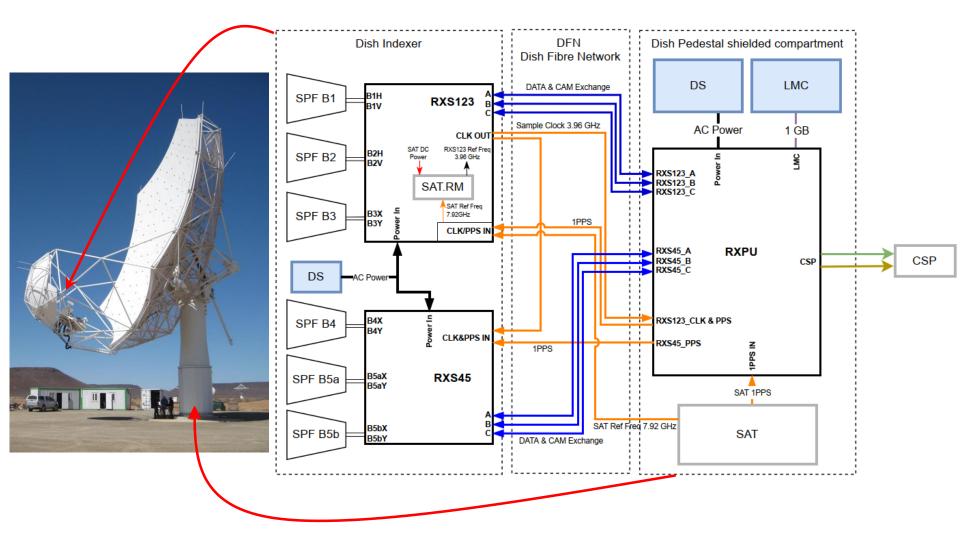

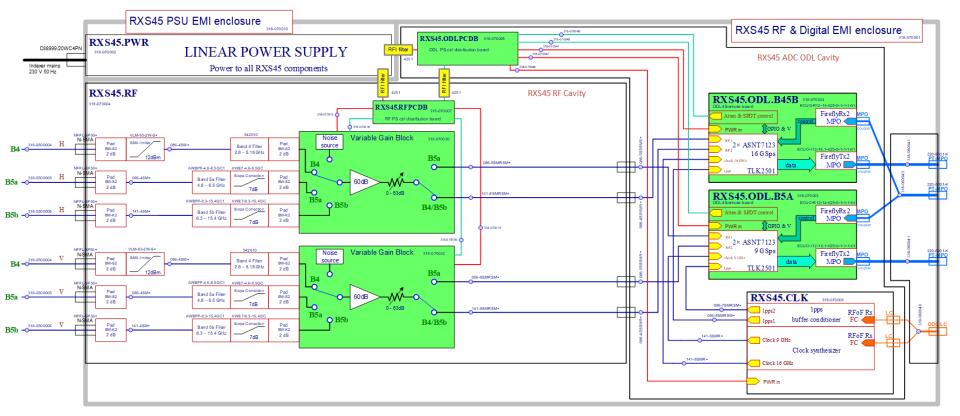

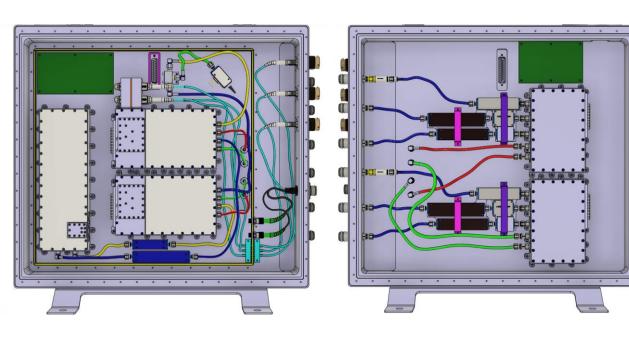

- Our design is based on the NRC design

- A PSU enclosure

**First Design**

- A main enclosure composed of two cavities

- RF cavity

- Digital cavity with two levels of EMI shielding

Stéphane Gauffre

# First Design

• Examples of realization

8

|           | Mechanical          | Electronics            | B5a          | B5b          | Comments / Risks                                                                                                                |

|-----------|---------------------|------------------------|--------------|--------------|---------------------------------------------------------------------------------------------------------------------------------|

| RXS45.RF  | 4 RF<br>enclosures  | 4 boards<br>(failures) | Simulation   | Simulation   | - Frequency response of B5b                                                                                                     |

| RXS45.CLK | 2 RF<br>enclosures  | 3 boards               | Measurements | Measurements |                                                                                                                                 |

| RXS45.ODL | 4 RF<br>enclosures  | 3 boards               | Measurements | Measurements | <ul> <li>RFI on site: &lt; 3 bits</li> <li>Additional bit needed for slope correction</li> <li>Adsantec: production?</li> </ul> |

| RXS45.PWR | 1 PSU<br>enclosure  | Simulation             |              |              | - Power loss too important                                                                                                      |

| RXS45     | 1 main<br>enclosure | B5b                    | Analysis     | Analysis     | <ul> <li>not ready for an end-to-end test</li> </ul>                                                                            |

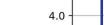

- Meeting at LAB with SKAO in May 2022

- $\Rightarrow$  New design with higher resolution ADC.

normalized ENOB @ 34 GS/s

ADC2 freqresp

ADC2

• 6-bit ADC at 32 GSps: first Nyquyst zone includes B5a & B5b:

Stéphane Gauffre

SKA-France Day 2022

40

50

Amplitude @ 34 GS/s

# **New Design**

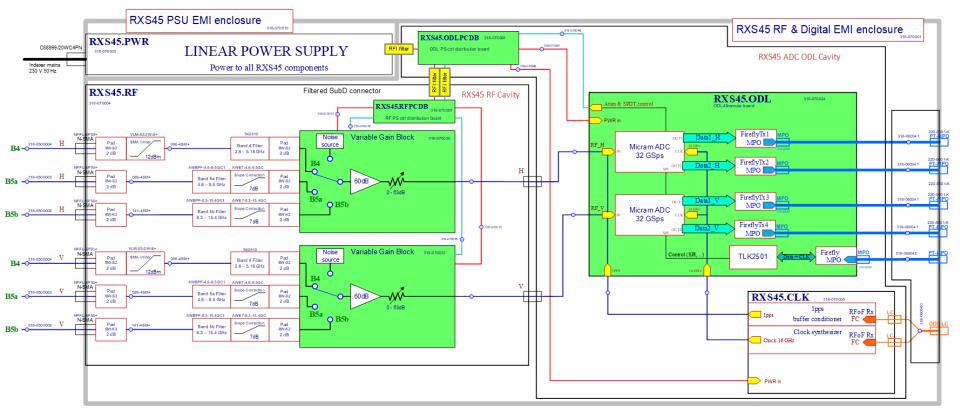

Adsantec solution ⇒ Micram solution

- Two ADC boards (B5a at 9 GSps and B5b at 16 GSps)

- Two RF boards with two outputs (one per band)

- > Two sampling clocks (9 GHz and 16 GHz)

## **New Design**

#### Adsantec solution ⇒ Micram solution

- Only one ADC board

- One output for RF board

- ➢ One clock at 16 GHz

## **New Design**

SPF B5a

SPF B5b

RXS45

SAT 1PPS

SAT

SAT Ref Fred 7 92 GH

# **Development Plan**

- Design changes

- Only one ADC board with two ADCs at 32 GSps: first Nyquyst zone includes B5a and B5b

- ➤ 48 outputs at 8 Gbps instead of 16 outputs at 16 Gbps  $\Rightarrow$  4×Tx12 (ADC outputs) and B04 (control and monitoring data)

- ➢ RF chain very similar to Adsantec solution

- Clock synthesizer board is simpler (only frequency multiplication by 4)

- Thermal analysis to be done (13 W each)

- Several shielding layers to be implemented

- Mechanical enclosure to be redesigned

- RXPU: Additional FPGA board to be designed for the B5 receiver interfacing with the Talon board (FPGA board developped by NRC)

- For CDR: use a Talon board (to be discussed with SKAO)

# **Development Plan**

- Goal is to pass the Critical Design Review (CDR) before end of 2023

- In one year, a lot of activities to be done: design, fabrication, test, document submission for reviews

- Two prototypes tested on site

- Detailed design review in june/july 2023: end-to-end test results in lab environment with EMC qualification (electromagnetic reverberation chamber at Airbus in Toulouse)

- Mechanical design based on NRC design with some changes from swedish team

- Support from FEDD for industrialization

- Funding from Nouvelle Aquitaine and CNRS (INSU)